Segmentation (gestion de la mémoire) – Wikipedia

Sous segmentation Comprendre la disponibilité contextuelle (registre d’adresses) des zones de mémoire dans le contexte des machines arithmétiques.

La segmentation était le seul moyen de traiter plus de 64 ki de mémoire de mots via un canal de stockage au moment des microprocesseurs 8 bits et 16 bits.

Au cours du développement des systèmes d’exploitation et des processeurs, la segmentation dans un mécanisme de protection et la pagination ont été développées.

Avec des processeurs 32 bits et ces systèmes d’exploitation 32 bits entièrement en charge (tels que Windows NT) et un logiciel utilisateur 32 bits, la segmentation de sa forme d’origine a été abolie.

Les processeurs avec segmentation contiennent généralement plusieurs registres de segmentation et matériel pour développer des adresses 16 bits basées sur le registre de segmentation aux lignes d’adresse physiquement existantes (souvent 20 ou 24).

L’implémentation sans support matériel interne a été effectuée par unité de gestion de la mémoire en tant que CI externe. Un exemple de cette dernière procédure est le garçon de jeu vendu par Nintendo dans les années 1990, dont les jeux contenaient souvent un MMU et donc malgré le Z80 Z. B. 1 Mib Rome utilisé.

À partir de la fin des années 1990, seul le but de la subdivision pour la mise en œuvre de mécanismes de protection ou de gestion de la mémoire virtuelle est resté. Selon le système d’exploitation et le matériel sous-jacent, divers attributs peuvent être affectés à un segment. Par exemple, les segments de programme, de données et de pile peuvent être déterminés. Pour l’architecture Intel x86, ces attributs résultent directement des registres de segmentation de l’Intel 8086, le processeur du premier PC IBM.

La gestion de la mémoire garantit alors, entre autres, que seules les commandes du segment du programme sont lues, mais aucune donnée n’est lue, ou que, inversement, les données du segment de données ne sont pas interprétées comme des commandes. Il est souvent possible également d’attribuer des segments de niveaux de privilèges, afin que les segments correspondants ne soient accessibles que par des programmes de certains niveaux de privilèges. Par exemple, vous pouvez protéger les données du système d’exploitation et les commandes contre l’accès par d’autres programmes. Souvent, le type d’accès (par exemple la lecture uniquement, l’écriture uniquement, pas d’accès) peut également être restreint. Certains systèmes permettent également des types d’accès dépendants du niveau de privilège.

Un segment est défini par deux valeurs:

- Début de segment, base ou base du segment: la première adresse mémoire contenue dans le segment

- Longueur du segment, limite de segment ou limite: le nombre d’adresses de mémoire successives que le segment comprend.

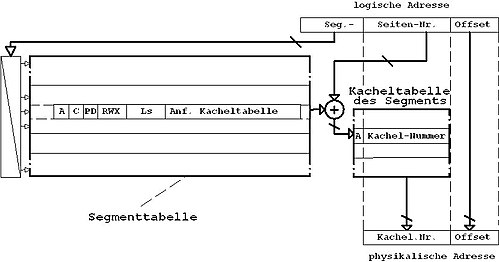

En règle générale, l’espace d’adresse physique est segmenté directement ou une salle d’adresse linéaire virtuelle qui représente la salle d’adresse physique. Un espace d’adressage logique si appelé est formé par la segmentation. Les adresses logiques sont divisées en un secteur de segment et un décalage. Le secteur du segment détermine directement ou indirectement, via un tableau de gestion du segment, le segment adressé et donc l’adresse et la longueur de démarrage du segment. Le décalage, par rapport au début du segment, spécifie le point de stockage dans ce segment.

Si l’adresse linéaire doit être déterminée à partir d’une adresse logique, les caractéristiques du segment de la base, de la longueur, du type, de la lecture / de l’écriture, etc. sont d’abord déterminées via le sélecteur de segment. Les propriétés du segment déterminées vérifient ensuite si l’accès à la mémoire est autorisé. De plus, le décalage est comparé à la longueur du segment pour garantir que l’accès se trouve dans les limites du segment. Si l’un de ces contrôles échoue, le traitement d’erreur (interruption, exception, etc.) est initié. Le décalage est ajouté à l’adresse de base du segment et se traduit par l’adresse linéaire. Si l’espace d’adresse linéaire n’est pas le physique, l’adresse linéaire est faite par une gestion de page ultérieure ( Anglais pagination ) converti en une adresse physique.

Ces changements d’adresse sont généralement pris en charge par des unités de gestion de la mémoire dans les ordinateurs modernes, qui sont intégrés dans de nombreux processeurs modernes.

Les processeurs X86 d’Intel de manière réelle [ Modifier | Modifier le texte source ]]

Dans le processeur 8086 et les X86 plus récents en mode réel, l’adresse du segment est calculée directement à partir du secteur du segment d’adresse logique. Tous les segments ont la longueur fixe de 64 kib. Une adresse logique est généralement écrite dans des programmes en mode réel: Segment : Compenser , où le segment et le décalage sont des nombres 16 bits et sont généralement spécifiés dans le système hexadécimal, par exemple: 2F10: 87A1 .

Cette adresse logique est convertie en une seule fois comme suit:

Adresse physiquement = Segmentselektor logiquement 16 + Compenser logiquement

Dans l’exemple, les résultats de l’adresse physique:

0x2f10 · 16 + 0x87a1 = 0x2f10 · 0x10 + 0x87a1 = 0x2f100 + 0x87a1 = 0x378a1

Avec cette adresse, vous pouvez étendre la largeur d’adresse physique à 20 bits, car l’adresse de segment 16 bits devient un nombre 20 bits par multiplication par 16, auquel le décalage est ajouté. Avec ces 20 bits, jusqu’à 1 MIB RAM peut être traité sur un processeur 16 bits. À strictement parler, même les nombres de 21 bits dans le calcul d’adresse peuvent résulter de la transmission en plus de l’addition, donc un peu plus d’une mémoire MIB peut être traitée. Pour des informations plus détaillées, une référence est faite à l’article High Memory Area et A20 Gate.

Paragraphe [ Modifier | Modifier le texte source ]]

À X86 Processeurs en mode réel, la zone de mémoire entre deux adresses est mentionnée comme un paragraphe, que vous obtenez lorsque vous augmentez ou réduisez le registre du segment d’une valeur exactement. [d’abord] Un paragraphe est de 16 octets. Le numéro de paragraphe est le nom de l’adresse de base sur laquelle commence cette zone de mémoire. [2] Le Paragprah est x86 et en mode réel spécifique.

Exemple:

Une adresse se compose du segment d’orthographe: décalage. La première adresse de segment possible d’un segment est l’adresse 0000: 0000, la seconde 0001: 0000. Dans le cas d’une adresse linéaire, cela correspondrait à l’adresse initiale 0x0 (décimal 0) et 0x10 (décimal 16). La zone de mémoire entre les deux est appelée paragraphe et reçoit exactement 16 octets par la méthode de calcul ci-dessus. Étant donné que chaque segment mesure 64 kib, les segments définis par ces deux adresses se chevauchent. Cependant, cela ne s’applique pas à la zone du paragraphe du segment inférieur.

Processeurs X86 d’Intel de manière protégée [ Modifier | Modifier le texte source ]]

À partir du processeur 80286 d’Intel, le mode soi-disant protégé a été introduit. Ici, les segments entre un octet et 64 kib (du 80386er jusqu’à 4 gib) peuvent être longs et commencer à n’importe quelle position d’octet dans la salle d’adresse linéaire. Chaque segment est décrit par une structure de données spéciale, appelée descripteur de segment. En plus de l’adresse de base du segment et de la durée du segment, un descripteur de segment contient également des informations sur les hommages au segment tels que le type de segment, le niveau de privilège et la lecture / écriture.

Les descripteurs de segment sont lus à partir de tables de descripteur se trouvant dans le RAM. Ces tableaux sont construits et gérés par le système d’exploitation. Le secteur du segment d’une adresse logique indique le tableau description et l’index d’un descripteur de segment dans le tableau. Les données requises pour le calcul d’adresse sont ensuite lues à partir du descripteur du segment sélectionné.

- ↑ https://thestarman.pcministry.com/asm/debug/segments.html#viz Supprimer le mystère du segment: décalage adressant # visualiser les segments qui se chevauchent

- ↑ “Programmation de l’assembleur” par Wolfgang Link, Franzis Verlag, ISBN 3-7723-8839-6, page 23

Recent Comments