Tranzystor-transystor logic-wikipedia

Homonimiczne artykuły patrz TTL.

Logika tranzystora-transystora Lub Ttl to rodzina obwodów logicznych używanych w elektronice, wynaleziona w 1961 roku [[[ Pierwszy ] James L. Buie (W) nazwa Logika tranzystorowa sprzężona z tranzystorem . Niezależnie, zainspirowany prezentacją [[[ 2 ] Od firmy FaiRichild na temat technik logicznych All-Transistor, Sylvania wyprodukowała pierwsze zintegrowane obwody sprzedaży TTL w 1963 roku. Opracowane i oferowane przez wielu producentów elektronicznych, rodzina TTL szybko stanowiła wiodący standard dla obwodów zintegrowanych w komputerach i urządzeniach cyfrowych.

Ta rodzina wykorzystuje technologię z nasyconym tranzystorem dwubiegunowym – w przeciwieństwie do niechętnych technologii tranzystorowych dwubiegunowych ( P. na zewnątrz. Rodzina ECL), z tranzystorem terenowym ( P. na zewnątrz. rodziny NMOS, PMOS, CMOS, HCMO) lub oporność i tranzystor ( P. na zewnątrz. W szczególności rodzina RTL). Jest to poprawa rodziny DTL Logic Doors ( Logika diod-transystor ) pojawił się w drugiej połowie lat 50. XX wieku. Dziś znika z powodu wysokiego zużycia energii (w porównaniu z obwodami CMOS).

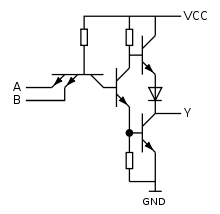

W prymitywnej wersji [[[ Pierwszy ] W [[[ 2 ] , Struktura elementarnych drzwi TTL (w tym przypadku odwrotna operator – nie) składa się z dwóch bipolarnych tranzystorów tego samego typu (zwykle typu NPN) i oporu, czyli :::

- I sprzężenie tranzystor , zamontowany we wspólnej podstawie, której nadajnik jest podłączony do wejścia do drzwi;

- I tranzystor d’Amplification et d’Inversion , zamontowany jako wspólny nadajnik, którego podstawa jest podłączona do kolekcjonera tranzystora sprzęgła, emitera do masy i kolekcjonera przy wyjściu drzwi;

- A opór , połączone między podstawą tranzystora sprzęgającego a zasilaczem (na biegunie dodatni w przypadku tranzystorów NPN), który zapewnia prąd niezbędny do działania drzwi.

Dwa tranzystory działają w trybie przełączania: każdy tranzystor jest albo nasycony (W TEN słabe) i równoważne przełącznikowi gospodarstwo rolne między jego kolekcjonerem a nadajnikiem zablokowany (I C nieistotne) i równoważne przełącznikowi otwarty Między jego kolekcjonerem a nadajnikiem.

Gdy do wejścia do drzwi zastosowano poziom niskiego napięcia poprzez opuszczenie prądu prądu do masy (sytuacja reprezentatywna stanu logicznego 0):

- Tranzystor sprzęgający jest nasycony prądem od oporu, który przekracza jego złącze przenoszącego podstawę

- amplifikacja i tranzystor odwrócenia jest blokowany, ponieważ jego napięcie przenoszenia podstawowego jest niewystarczające

- Obwód zewnętrzny podłączony do gniazdka drzwi może wytwarzać poziom wysokiego napięcia (reprezentatywny stanu logicznego 1).

Gdy prąd wytwarzany przez wejście do drzwi nie jest spuszczony w kierunku masy lub przy stosowaniu poziomu wysokiego napięcia na tym wejściu (reprezentatywna sytuacja stanu logicznego 1):

- Tranzystor sprzęgania jest zablokowany † Ponieważ jego napięcie przenoszącego podstawę jest niewystarczające lub ujemne ‡

- Amplifikacja i tranzystor odwrócenia jest nasycony prądem wynikającym z rezystancji, który przekracza połączenie z kołnierzem bazowym tranzystora sprzęgającego

- Tranzystor wzmacniający i odwrócenia wymaga niskiego poziomu napięcia poza drzwiami (reprezentatywne dla stanu logicznego 0) poprzez wyczerpanie prądu z obwodu zewnętrznego w kierunku masy.

Uwagi :

† : blokowanie tranzystora sprzężenia odpowiada i I Nikt z inwersją roli jego nadajnika i jego kolektora (c) ze względu na jego szczególną polaryzację. Ta blokada występuje bez znaczącej de-nasycation tranzystora [[[ Pierwszy ] , który zapewnia bardzo krótkie czasy przełączania.

‡ : Aby zapewnić blokowanie tranzystora sprzęgła podczas odwracania roli jego nadajnika i kolektora poprzez zastosowanie wysokiego napięcia (np. 5 5 W ) Przy wejściu do drzwi jest wytwarzane tak, aby jego przeciwna moc była bardzo niska.

Aby utworzyć operatora logicznego nie-i-i użycia, używamy wieloemijalnego tranzystora sprzęgania, którego każdy nadajnik jest podłączony do wejścia obwodu, aby ten tranzystor nie został zablokowany, a zatem wytwarza niski poziom Wylot drzwi (stan logiczny 0), że gdy wszystkie wejścia są na wysokim poziomie (stan logiczny 1).

Zatem zasadowe połączenia tranzystora sprzęgającego wykonują logiczną operację i jak obwód logiczny z diodami ( P. na zewnątrz. DTL), następnie amplifikacja i odwrócenie tranzystor wykonują operowanie braku logicznego.

Na przykład dla trzech danych wejściowych logicznych a, b i c wytwarzających stan wyjścia logicznego y, tranzystor sprzęgający najpierw wykonuje operację x = a.b.c, a następnie amplifikacja i odwrócenie tranzystor realizuje operację y = ¬ X = ¬ ( ABC ) .

Aby utworzyć operatora logicznego, którego nie jest ubiegłym, których kolekcjonerzy wzmacniaczy i tranzystorów odwracania są ze sobą powiązane, tak że napięcie wyjściowe jest wymuszane na niskim poziomie (warunek logiczny 0), gdy tylko napięcie co najmniej jeden z jednego z Wpisy są na wysokim poziomie (stan logiczny 1).

Zatem tranzystory wzmacniające i odwracające zdają sobie sprawę z operacji logicznej nie, razem, razem, logicznej operacji i w sposób bezpośredniego obwodu sprzężenia ( P. na zewnątrz. Dctl).

Na przykład dla trzech wpisów logicznych A, B i C wytwarzających stan wyjścia logicznego y, drzwi nie przeprowadzają najpierw operacji u = ¬ A , V = ¬ B i w = ¬ C , wówczas wzajemne połączenie tranzystorów wzmocnienia i odwracania realizuje operację y = U.V.W = ¬ A . ¬ B . ¬ C = ¬ ( A+B+C ) .

Przeprowadzamy działalność logiczną i nie-nie, bezpośrednio łącząc dwa poprzedzające nieporęczne montaże.

W praktyce, w różnych seriach obwodów TTL, które oferują, od samego początku producenci wdrażają tę prymitywną strukturę, zapewniając ulepszenia mające na celu zwiększenie jego wydajności (prędkość, zużycie, odporność na hałas, wentylatory, wentylatory itp.) .

W szczególności tranzystor wzmacniający i odwrócenia nie jest już podłączony bezpośrednio do wyjścia obwodu logicznego, ale pilotuje podłogę wzmacniacza push-up (Totem-Pole) lub z otwartym kolektorem.

Systematyczna obecność tej podłogi wyjściowej doprowadziła do normalizacji progów napięcia poziomów logiki TTL do wartości wyższych niż prymitywna struktura Buie (0,8 W i 2 W [[[ 4 ] zamiast 0,2 W i 0,8 W około [[[ Pierwszy ] Odpowiednio dla niskich i wysokich poziomów).

Najnowsza seria obwodów TTL (LS, F, AS, ALS) wdraża struktury, w których sprzężenie wejść nie jest już wykonywane przez tranzystor, ale przez montaż oparty na diodach Schottky. Niemniej jednak, ponieważ te serie pochodzą bezpośrednio z pierwszej serii TTL i odtwarzają podstawowe cechy i dużą część struktury, producenci nadal kwalifikowali je jako „TTL”.

Żywność [[[ modyfikator |. Modyfikator i kod ]

Technologia TTL jest znormalizowana dla Napięcie zasilania (W CC ) z 5 W .

Tolerancja napięcia zasilania wynosi ± 5 % (± 0,25 W ) dla serii komercyjnych i przemysłowych (cechy i gwarantowane działanie między 0 ° C. I +70 ° C. ) i ± 10 % (± 0,5 W ) dla serii wojskowych (cechy i operacja gwarantowane pomiędzy −55 ° C. I +125 ° C. ).

Obecne spożycie żywności zależy od złożoności obwodu i serii TTL, do której należy. Zużycie to różni się w zależności od temperatury, stanów logicznych i prądów krążących przez dane wejściowe i wyjścia. Wzrasta również wraz z częstotliwością przemian logicznych, gdy częstotliwość ta staje się wysoka (wszystkie inne warunki ustawione gdzie indziej, średnie zużycie pozostaje praktycznie stałe na niskich częstotliwościach).

Obecne przykłady konsumpcji:

| Okrążenie | I Cch | I CCl | Jednostka | ||

|---|---|---|---|---|---|

| typ. | Max. | typ. | Max. | ||

| SN7400 | 4 | 8 | dwunasty | 22 | I |

| SN74LS00 | 0,8 | 1.6 | 2.4 | 4.4 | I |

| SN74S00 | dziesięć | 16 | 20 | 36 | I |

I Cch : prąd zasilania, wyjścia w wysokim stanie

I CCl : prąd zasilania, wyjścia o niskim poziomie

Typ. : typowa wartość; Max. : maksymalna wartość

Źródło: Arkusz danych obwodów SN74X00 (4 drzwi NAND z dwoma wpisami), Texas Instruments, 1983

Napięcia i prądy wejściowe i wyjściowe [[[ modyfikator |. Modyfikator i kod ]

Sygnał TTL jest zdefiniowany jako Niski poziom logiki między 0 W I 0,8 W (W . ) i jak Wysoki poziom logiczny pomiędzy 2.0 W i 5 W (W ICH ) [[[ 5 ] . Po zastosowaniu do wejście Z obwodu TTL sygnał zgodnie z tymi plażami napinającymi gwarantuje prawidłową interpretację odpowiednich poziomów logicznych. Poziomy te różnią się nieznacznie między różną serią i według producenta (na przykład v . jest zredukowane do 0,7 W Dla SN54LS00 z Texas Instruments).

Ponadto, aby zagwarantować względną odporność na szum, sygnały logiczne wytwarzane przez Wyjście Obwód TTL odpowiada mniejszym określonym napięciu plaż: minimalne napięcie wyjściowe na wysokim poziomie v OH jest większy niż V ICH oraz maksymalne napięcie wyjściowe na niskim poziomie V Ol jest niższy niż V . . Obwód obsługuje hałas, tym ważniejsze jako różnice między v OH i 5 ICH z jednej strony (margines hałasu w wysokim stanie) i pomiędzy v . i 5 Ol Z drugiej strony (margines hałasu w niskim stanie) jest wysoki.

Przykład poziomów napięcia, określony dla drzwi logicznych TTL fairchild półprzewodnikowy [[[ 4 ] , z odpowiednimi marginesami szumu:

| Limity, w W | |||||

|---|---|---|---|---|---|

| Komercyjna seria TTL (0 ° C do +70 ° C) |

Wejście | Wyjście | |||

| W . | W ICH | W Ol | W OH | ||

| 74 | Standardowy TTL | 0,8 | 2.0 | 0,4 | 2.4 |

| 74H | Szybki TTL | 0,8 | 2.0 | 0,4 | 2.4 |

| 74l | TTL o niskiej mocy | 0,8 | 2.0 | 0,3 | 2.4 |

| 74s | Schottky Ttl | 0,8 | 2.0 | 0,5 | 2.7 |

| 74ls | Schottky TTL o niskiej mocy | 0,8 | 2.0 | 0,5 | 2.7 |

| Margines hałasu, w W | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| na niskim poziomie (v . -W Ol ) | na wysokim poziomie (v OH -W ICH ) | ||||||||||

| Z : | W kierunku : | Z : | W kierunku : | ||||||||

| 74 | 74H | 74l | 74s | 74ls | 74 | 74H | 74l | 74s | 74ls | ||

| 74 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 | 74 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 | 74H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74l | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 | 74l | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 74s | 0,3 | 0,3 | 0,3 | 0,3 | 0,3 | 74s | 0,7 | 0,7 | 0,7 | 0,7 | 0,7 |

| 74ls | 0,3 | 0,3 | 0,3 | 0,3 | 0,3 | 74ls | 0,7 | 0,7 | 0,7 | 0,7 | 0,7 |

| Limity, w W | |||||

|---|---|---|---|---|---|

| Wojskowa seria TTL (-55 ° C do +125 ° C) |

Wejście | Wyjście | |||

| W . | W ICH | W Ol | W OH | ||

| 54 | Standardowy TTL | 0,8 | 2.0 | 0,4 | 2.4 |

| 54H | Szybki TTL | 0,8 | 2.0 | 0,4 | 2.4 |

| 54l | TTL o niskiej mocy | 0,7 | 2.0 | 0,3 | 2.4 |

| 54s | Schottky Ttl | 0,8 | 2.0 | 0,5 | 2.5 |

| 54ls | Schottky TTL o niskiej mocy | 0,7 | 2.0 | 0,4 | 2.5 |

| Margines hałasu, w W | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| na niskim poziomie (v . -W Ol ) | na wysokim poziomie (v OH -W ICH ) | ||||||||||

| Z : | W kierunku : | Z : | W kierunku : | ||||||||

| 54 | 54H | 54l | 54s | 54ls | 54 | 54H | 54l | 54s | 54ls | ||

| 54 | 0,4 | 0,4 | 0,3 | 0,4 | 0,4 | 54 | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54H | 0,4 | 0,4 | 0,3 | 0,4 | 0,4 | 54H | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54l | 0,5 | 0,5 | 0,4 | 0,5 | 0,5 | 54l | 0,4 | 0,4 | 0,4 | 0,4 | 0,4 |

| 54s | 0,3 | 0,3 | 0,2 | 0,3 | 0,3 | 54s | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 |

| 54ls | 0,4 | 0,4 | 0,3 | 0,4 | 0,3 | 54ls | 0,5 | 0,5 | 0,5 | 0,5 | 0,5 |

Warunki, w których te poziomy wyjściowe są zdefiniowane, różnią się w zależności od serii TTL i rozważanym stanu logicznym i mogą się nieznacznie różnić w zależności od producenta. W szczególności specyfikacje określają:

- I Ol , maksymalna wartość prądu wytworzona przez wyjście do określonego limitu napięcia v Ol (niski warunek)

- I OH , maksymalna wartość (w wartości bezwzględnej) prądu wytwarzanego przez wyjście do określonego limitu napięcia v OH (Wysoki warunek)

- I . , maksymalna wartość (w wartości bezwzględnej) prądu wynikającego z aplikacji na wejściu niskiego poziomu logiki

- I ICH , maksymalna prądowa wartość wynikająca z aplikacji na wejściu wysokiego poziomu logicznego.

NB: Z konwencji prądy są ujemne, gdy opuszczają komponent.

Wejście do drzwi TTL emituje znaczący prąd w niskim stanie (i . ) i pochłania bardzo niski prąd w stanie wysokim (i ICH ), kilka dziesiątek µA do maksimum. Ponadto pasożytniczy pojemność wejścia musi być załadowana lub rozładowana przez prąd podczas przejściów. Zatem, aby zagwarantować zgodność z poziomami logicznymi i ograniczyć czas trwania przejść, wyjście TTL podłączone do jednego lub więcej wejść TTL musi być w stanie spuścić znaczący prąd do niskiej masy i wytwarzać znacznie niższy prąd (ale mimo to znaczący) w Wysoki stan.

W rezultacie poziomy napięcia wyjściowego obwodów TTL są ogólnie zdefiniowane dla znacznie wyższych maksymalnych prądów w niskim stanie (i Ol ) to w wysokim stanie (i OH ).

Istnieją jednak wyjątki, takie jak znaczki TTL (bufory, angielskie) i pilotów linii transmisji (sterowniki linii, w języku angielskim), które są w stanie zapewnić duży prąd w stanie wysokim. Porównywać :

| Obwód TTL | Funkcjonować | Określone limity | |

|---|---|---|---|

| I OH @ W OH | I Ol @ W Ol | ||

| DM74LS04 | 6 drzwi inversors (operator nie), Z wejściami o histereza |

−0,4 I @ 2.7 W | 4 I @ 0.4 W 8 I @ 0,5 W |

| DM74LS240 | 2 × 4 tampony falowniki z wpisami do histerezy i wycieczek do trzech stanów |

−1 I @ 2.7 W −3 I @ 2.4 W −15 I @ 2.0 W |

dwunasty I @ 0.4 W 24 I @ 0,5 W |

H = wyjście na wysokim poziomie (1 logika)

L = wyjście na niskim poziomie (0 logika)

Przykład poziomów napięcia i prądu określone dla drzwi logicznych instrumentów Texas [[[ 8 ] :

| Seria Ttl |

Prądy w I | Napięcia w W | ||||||

|---|---|---|---|---|---|---|---|---|

| Wyjście | Wejście | Wyjście | Wejście | |||||

| I OH | I Ol | I ICH | I . | W OH | W Ol | W ICH | W . | |

| 54/74 | -0.4 | 16 | 0,04 | -1.6 | 2.4 | 0,4 | 2.0 | 0,8 |

| 54H/74H | -0,5 | 20 | 0,05 | -2 | 2.4 | 0,4 | 2.0 | 0,8 |

| 54l | -0,1 | 2 | 0,01 | -0,18 | 2.4 | 0,3 | 2.0 | 0,7 |

| 74l | -0.2 | 3.6 | 0,01 | -0,18 | 2.4 | 0,4 | 2.0 | 0,7 |

| 54ls | -0.4 | 4 | 0,02 | -0.4 | 2.5 | 0,4 | 2.0 | 0,7 |

| 74ls | -0.4 | 8 | 0,02 | -0.4 | 2.7 | 0,5 | 2.0 | 0,8 |

| 54s | -Pierwszy | 20 | 0,05 | -2 | 2.5 | 0,5 | 2.0 | 0,8 |

| 74s | -Pierwszy | 20 | 0,05 | -2 | 2.7 | 0,5 | 2.0 | 0,8 |

| 54AS/74AS | -2 | 20 | 0,02 | -0,5 | 2.5 | 0,5 | 2.0 | 0,8 |

| 54als | -0.4 | 4 | 0,02 | -0,1 | 2.5 | 0,4 | 2.0 | 0,8 |

| 74als | -0.4 | 8 | 0,02 | -0,1 | 2.5 | 0,4 | 2.0 | 0,8 |

Te granice napięć i prądów umożliwiają zdefiniowanie zarys (lub fan-out, w języku angielskim), który jest maksymalną liczbą drzwi logicznych, w których można podłączyć wydanie drzwi logicznych.

Poniższa tabela, która dotyczy drzwi logicznych TTL z Texas Instruments [[[ 8 ] , rozróżnia rodzaj na wysokim poziomie niskiego poziomu, aby móc rozważyć połączenie drzwi należących do różnych serii TTL:

| Poziomy logiczne, w zależności od serii TTL | ||||||||

|---|---|---|---|---|---|---|---|---|

| Z : | Poziom logika |

W kierunku : | ||||||

| 54 74 |

54H 74H |

54l 74l |

54ls 74ls |

54s 74s |

54as 74as |

54als 74als |

||

| 54 74 |

H | dziesięć | 8 | 40 | 20 | 8 | 20 | 20 |

| L | dziesięć | 8 | 88,89 | 40 | 8 | 32 | 160 | |

| 54H 74H |

H | 12.5 | dziesięć | 50 | 25 | dziesięć | 25 | 25 |

| L | 12.5 | dziesięć | 111.11 | 50 | dziesięć | 40 | 200 | |

| 54l | H | 2.5 | 2 | dziesięć | 5 | 2 | 5 | 5 |

| L | 1.25 | Pierwszy | 11.11 | 5 | Pierwszy | 4 | 20 | |

| 74l | H | 5 | 4 | 20 | dziesięć | 4 | dziesięć | dziesięć |

| L | 2.25 | 1.8 | 20 | 9 | 1.8 | 7.2 | 36 | |

| 54ls | H | dziesięć | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 2.5 | 2 | 22.22 | dziesięć | 2 | 8 | 40 | |

| 74ls | H | dziesięć | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 5 | 4 | 44,44 | 20 | 4 | 16 | 80 | |

| 54s 74s |

H | 25 | 20 | 100 | 50 | 20 | 50 | 50 |

| L | 12.5 | dziesięć | 111.11 | 50 | dziesięć | 40 | 200 | |

| 54as 74as |

H | 50 | 40 | 200 | 100 | 40 | 100 | 100 |

| L | 12.5 | dziesięć | 111.11 | 50 | dziesięć | 40 | 200 | |

| 54als | H | dziesięć | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 2.5 | 2 | 22.22 | dziesięć | 2 | 8 | 40 | |

| 74als | H | dziesięć | 8 | 40 | 20 | 8 | 20 | 20 |

| L | 5 | 4 | 44,44 | 20 | 4 | 16 | 80 | |

H: wysoki poziom; L: niski poziom

Szare pola tabeli odpowiadają wejściom i wyjściom drzwi logicznych należących do tej samej serii TTL.

Biorąc pod uwagę wydanie drzwi logicznych, każde podłączone do niego dane wejściowe zużywa ułamek tego rodzaju. Aby montaż był prawidłowy, konieczne jest, aby suma tych ułamków nie przekroczyła dostępnych rodzajów, ani na wysokim poziomie, ani na niskim poziomie.

Na przykład, zgodnie z poprzednią tabelą, uwolnienie drzwi 74L można połączyć jednocześnie z wejściem do A drzwi 74 godziny i trzy 74S drzwi, ponieważ:

- Na wysokim poziomie (h): 1 – Pierwszy 4 – 3 dziesięć ≥ 0

- Na niskim poziomie (L): 1 – Pierwszy 1.8 – 3 7.2 ≥ 0

I odwrotnie, nie jest możliwe podłączenie wpisu sześć 74 -HOUR Drzwi przy wyjściu drzwi 74L, ponieważ jeśli masz 1 – 6 8 ≥ 0 Na wysokim poziomie mamy 1 – 6 4 <0 na niskim poziomie.

Zauważony : Życzliwość nie jest zdefiniowana w odniesieniu do liczby wpisów fizyczny obwody logiczne, ale w stosunku do liczby równowartość konwencjonalnych wpisów do drzwi logicznych, z punktu widzenia gwarantowanych właściwości elektrycznych. Dlatego musimy w szczególności wziąć pod uwagę fakt, że bufor może przedstawić milszy niż konwencjonalne drzwi logiczne lub że wprowadzanie złożonego obwodu logicznego można podłączyć do kilku wejść wewnętrznych drzwi logicznych.

Dynamiczne zachowanie [[[ modyfikator |. Modyfikator i kod ]

Elektroniczne systemy cyfrowe charakteryzują się różnymi terminami w propagacji sygnałów poprzez obwody logiczne i ich połączenia. Terminy te ograniczają ich prędkość roboczą i prawdopodobnie wpłyną na zachowanie sekwencyjnych obwodów logicznych.

Jednak te terminy nadają obwodom względną odporność na krótkie pasożytnicze impulsy.

Zauważamy, że drzwi TTL Schottky (seria 74S) są szybsze niż standardowe drzwi TTL (seria 7400), ale są wrażliwe na pasożytnicze impulsy pasożytnicze.

Terminy propagowania sygnałów w tym samym obwodzie zintegrowanym zależą od jego złożoności i zastosowanej serii TTL. Mogą się różnić w zależności od znaczenia przejść (ilość lub potomek) i w zależności od warunków użytkowania (temperatura, napięcie zasilania, obciążenie zewnętrzne).

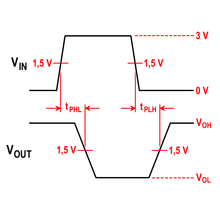

Definiujemy je w następujący sposób:

- T Phl = Czas propagacji sygnału logicznego wytwarzającego wysokie przejście → niskie na wyjściu

- T Plh = Czas propagacji sygnału logicznego wytwarzającego niskie przejście → wysokie na wyjściu

Przykłady czasu propagacji określone dla drzwi innych niż (’00) z różnych serii TTL:

| Seria TTL | 54/7400 | 54/74H00 | 54/74S00 | 54/74LS00 | Jednostka | ||||

|---|---|---|---|---|---|---|---|---|---|

| Wartości | Min | Max | Min | Max | Min | Max | Min | Max | |

| T Phl | – | 15 | – | dziesięć | 2.0 | 4.5 | – | dziesięć | ns |

| T Plh | – | 22 | – | dziesięć | 2.0 | 4.5 | – | dziesięć | ns |

| Warunki | C L = 15 pf R L = 400 Oh |

C L = 15 pf R L = 280 Oh |

C L = 15 pf R L = 280 Oh |

C L = 15 pf – |

|||||

- Według Texas Instruments [[[ 9 ]

| Porte ttl | SN54/7400 | SN54/74S00 | SN54/74LS00 | Jednostka | |||

|---|---|---|---|---|---|---|---|

| Wartości | typ. | Max. | typ. | Max. | typ. | Max. | |

| T Phl | 7 | 15 | 3 | 5 | dziesięć | 15 | ns |

| T Plh | 11 | 22 | 3 | 4.5 | 9 | 15 | ns |

| Warunki | C L = 15 pf R L = 400 Oh |

C L = 15 pf R L = 280 Oh |

C L = 15 pf R L = 2 kΩ |

||||

Wartości mierzone w t A = 25 ° C. (temperatura pokojowa) i v CC = 5 W

C L , R L : obciążenie testowe podłączone do wyjścia drzwi

min. : minimalna wartość; Typ. typowa wartość; Max. : maksymalna wartość

Czasy przejścia sygnału przy wyjściu drzwi logicznych interweniujących w terminach propagacji zwiększa się, gdy obciążenie podłączone do wyjścia są ważniejsze:

Raty ustalania poziomów logicznych przesyłanych między wyjściem TTL a wejściami, które są tam podłączone, zależą od implementacji zintegrowanych obwodów (geometria przewodów elektrycznych, charakter izolatorów) i charakterystyka elektryczna tego wyjścia (wyjście) i tych wpisów (Lence).

W przypadku połączeń dokonanych na dość niskie odległości, sterowniki wiążące mogą być asymilowane z zdolnościami pasożytowymi, a sygnały nie podlegają znaczącej degradacji specyficznej dla linii przesyłowych (w szczególności odbicia, a zwłaszcza nadmierne asychlowanie – degradacje są faworyzowane przez zmienną naturę impedancji wejściowych i wyjściowych TTL TTL obwody, które nie mogą zatem trwale odpowiadać stałej charakterystycznej impedancji linii przesyłowej). Czasy przejścia przesyłanych sygnałów zależą z jednej strony, od suma tych pasożytniczych zdolności i zastosowań wejściowych TTL, a z drugiej strony, na bieżącym wyjściu jest w stanie wytwarzać w celu załadowania i rozładunku zestawu tych zdolności . Przejścia są tym bardziej krótkie, ponieważ zdolności są niskie i że prądy są wysokie.

Przykład maksymalnych długości połączeń bez znaczących efektów specyficznych dla linii przesyłowych dla różnych serii TTL (według Fairchild [[[ 4 ] ):

| Seria TTL | Czas na wspinać się |

Czas na zejście |

Długość maksymalny |

|---|---|---|---|

| 54/74 | 6 do 9 ns | 4 do 6 ns | 45 cm |

| 54/74H, 54/74LS |

4 do 6 ns | 2 do 3 ns | 22.5 cm |

| 54/74s | 1,8 do 2,8 ns | 1.6 do 2.6 ns | 19 cm |

(Wartości odnotowane dla prędkości propagacji 5.6 ns/m , na obwodzie wydrukowanym w epoksydowej stałej stałej ε stałej R = 4.7)

Oprócz kilku konkretnych odniesień (np. 74S140 Stamps) i najnowszej serii (w szczególności w i in.), Obwody logiczne TTL nie zostały zaprojektowane tak, aby były połączone za pomocą linii przesyłowych, pomimo urządzeń wewnętrznych dodanych do niektórych ich efektów (np. Diody zaciskowe obecne na wejściach w celu wchłaniania onoscation). Dlatego wymagają specjalnych wysiłków projektowych, gdy długość połączeń staje się zbyt ważna.

Kompatybilność TTL [[[ modyfikator |. Modyfikator i kod ]

Kiedy rodzina obwodów logicznych opartych na technologii różnej od technologii TTL ma charakterystykę zgodnie z określonymi limitami wspólnymi dla obwodów TTL (napięcia i prądów), nazywa się ją ” Kompatybilny TTL ». Obwody te zostały zaprojektowane w celu zastąpienia obwodów technologii TTL przy jednoczesnym poprawie wydajności (odporność na hałas, zużycie energii elektrycznej, prędkość itp.) Lub być bezpośrednio połączone. W ich przypadku nadal możemy o tym rozmawiać sygnały Ttl to Poziomy logiczne TTL, ale więcej niż obwody Ttl.

Przykłady TTL (ACT), Advanced Bicmos Technology (LVT) i Advanced LVT (ALVT), rodziny kompatybilnych z HCMOS TTL (HCT), Advanced CMOS TTL (ACT), Advanced BICMOS Technology (ABT), technologii niskiego napięcia (LVT) i Advanced LVT (ALVT).

Obwody rodzin LVT i ALVT, wykonane w technice BICMOS, są kwalifikowane jako kompatybilne z LVTTL (niskie napięcie TTL lub „niskie napięcie TTL” w języku francuskim) ze względu na ich zmniejszone napięcie zasilania do 3,3 W (zamiast 5 W Dla rodziny TTL) i kompatybilność TTL ich poziomów logicznych. Niemniej jednak niektóre z tych obwodów posiadających zdolność do działania przy jeszcze niższych napięciach mocy (np. 2.5 W [[[ dziesięć ] ), tracą zgodność TTL, gdy są stosowane w tych warunkach.

Jednak gdy na to pozwalają szczególne okoliczności, możliwe jest, że obwód logiczny, którego cechy nie jest w pełni zgodne ze specyfikacjami obwodów TTL, może być nadal bezpośrednio połączony. Na przykład wraz ze zmniejszeniem tolerancji drzwi TTL i drzwi 74LVC mogą być bezpośrednio połączone w 2.5 W oraz wydanie drzwi 74HC dostarczonych w 5 W może bezpośrednio kontrolować wejście do drzwi TTL (odwrotność nie jest dozwolona).

- Ta rodzina komponentów łączy dobrą prędkość przełączania z niskim czasem transferu.

- Odporność na pasożyty jest dobra, pod warunkiem, że możesz oddzielić zasilanie jak najbliżej każdego obwodu za pomocą kondensatora filtra.

- Domyślnie wejście do powietrza (bez poziomu napięcia na zewnątrz) znajduje się w stanie logicznym „1” (przepływa tylko znaczące prąd, gdy jest zmuszony do stanu logicznego „0”, gdzie zachowuje się równoważność odporności wycofania do v CC = 5 W ). Niemniej jednak producenci zalecają zawsze podłączanie wejścia pozostającego w stanie logicznym „1” do stałego potencjału większego niż 2,5 W , w szczególności, aby nie degradować dynamicznej wydajności innych wpisów w drzwiach logicznych TTL.

- Dostarczenie obwodów TTL musi być precyzyjne: +5 V ± 5%, w porównaniu z obwodami CMOS, które mają znacznie większy zakres mocy (od +3 do +18 V). W przypadku niezgodności z tym imperatywem istnieje w najlepszym razie nieregularne działanie obwodu, aw najgorszym przypadku częściowe lub całkowite zniszczenie obwodu.

- Technika dwubiegunowa jest dużym konsumentem prądu elektrycznego; Wspomnienia TTL są z pewnością szybkie, ale nie można ich zaoszczędzić przez długi czas w przypadku przerwy w zasilanie.

- Nie możemy przekazywać sygnałów emitowanych przez obwody TTL bez dodatkowych obwodów transmisyjnych na dużych odległościach bez strat: maksymalna długość około 15 M .

W latach po wynalezieniu technologii TTL różni producenci obwodów zintegrowanych zaproponowali stosunkowo zróżnicowane komponenty TTL pod względem konfiguracji i oznaczenia. Zainicjowane przez Texas Instruments, seria 5400 obwodów i jej deklinacja 7400 (dla obecnych zastosowań komercyjnych i przemysłowych, w przeciwieństwie do bardziej wymagających przestrzeni i zastosowań wojskowych), a następnie nałożyły się jako wspólne odniesienie.

Od tego czasu powołanie obwodu rodziny TTL na ogół składało się z liczby 74 lub 54, a prawdopodobnie po jednej lub więcej liter odpowiadających serii powiązanej z dużą ewolucją technologii TTL (brak listu dla standardu serii standard ) Następnie liczba dwóch do czterech cyfr odpowiadających funkcji logicznej przeprowadzonej przez obwód. Może zawierać określony prefiks dla producenta (np. SN dla instrumentów Texas) i sufiks, który zawiera dodatkowe informacje, takie jak rodzaj obudowy (np. Dla plastikowych skrzynek zanurzeniowych) lub wariant w specyfikacji.

Główna seria należąca do rodziny TTL to:

- Ttl [[[ 11 ] W [[[ dwunasty ] : Standardowa seria

- Ttl-l [[[ 11 ] (Niska moc): seria o niskim zużyciu

- TTL-H [[[ 4 ] (Duża prędkość): Quick Series

- TTL-s [[[ 11 ] W [[[ dwunasty ] (Schottky): Szybka seria w Transistors Schottky

- TTL-LS [[[ 11 ] W [[[ dwunasty ] (Low Power Schottky): Połączenie technologii L i S, jest to najbardziej powszechna rodzina

- TTL-f [[[ 13 ] (Szybka: Fairchild Advanced Schottky Technology)

- Ttl-as [[[ 14 ] (Advanced Schottky): Ulepszona wersja serii S

- TTL-LAS [[[ 15 ] (Advanced Low Power Schottky): Ulepszona wersja serii LS

W celu połączenia zalet technik dwubiegunowych (prędkości) i CMO (niskie zużycie, szeroki zakres napięcia) inżynierowie zaprojektowali inne rodzaje obwodów logicznych zawierających funkcje klasycznej serii TTL.

W porządku chronologicznym:

- HCMOS 74HCXX (Niezgodne z TTL, V Logiczne poziomy CC = 2 V do 6 W , minimalny czas propagacji = 20 ns dla v CC = 6 V, ponad 100 ns dla v CC = 2 V).

- TTL kompatybilny HCMOS 74HCTXX (W CC = 4,5 W przy 5.5 W , typowy czas propagacji = 20 ns).

- Advanced Bicmos 74ABTXX (Kompatybilny z TTL, łączy CMO i technologie dwubiegunowe dla niskiego zużycia i prądów wysokiej wyjściowych, typowy czas propagacji = 3 ns)

- Zaawansowane HCMO 74ahcxx (Niezgodne z poziomami logiki TTL, szybciej niż 74HCXX, typowy czas propagacji = 5 ns)

- Zaawansowane HCMO Kompatybilny TTL 74ahctxx (szybciej niż 74HCTXX, typowy czas propagacji = 5 ns)

- Technologia Bicmos o niskim napięciu 74lvtxx (TTL kompatybilny z napięciem mocy 3,3 V, łączy CMO i technologie dwubiegunowe, typowy czas propagacji = 2 ns)

- Zaawansowana technologia Bicmos o niskim napięciu 74Alvtxx (szybciej niż 74lvtxx, typowy czas propagacji = 1,5 ns)

Obwód 7400 [[[ modyfikator |. Modyfikator i kod ]

Obwód 7400 to czterokrotny „nie-i” (NAND).

Karmimy obwód w następujący sposób: v CC Na styku 14 (+5 W ) i masa na wrzeciona 7.

Każde z czterech drzwi można użyć w następujący sposób:

- Drzwi NAND-1, wejścia A i B na szpilkach 1 i 2, wyjściowe na wrzeciona 3.

- Drzwi NAND-2, wejścia A i B na szpilkach 4 i 5, wychodzące na wrzecionie 6.

- Drzwi NAND-3, wejścia A i B na szpilkach 9 i 10, wychodzące na wrzecionie 8.

- Drzwi Nand-4, wejścia A i B na szpilkach 12 i 13, wychodzące na wrzeciona 11.

Oczywiście drzwi są niezależne od siebie, jeśli niektóre drzwi nie są używane, możemy podłączyć ich wpisy A i B z +V CC (lub masa) i pozostaw wyjście „w powietrzu”.

Uwaga: wpisy A i B są ze sobą wymienne.

7490 licznik [[[ modyfikator |. Modyfikator i kod ]

Licznik 7490 to dziesiętny miernik asynchroniczny (złożony z namiotu 4 jk).

- (W) List US3283170a Stworzony 8 września 1961 r. Przez Jamesa L. Buie

- (W) Nowe formy logiki-transistor Par R. Beeson i H. Ruegg – 1962 IEEE Międzynarodowe konferencje obwodów stałego stanu stałego. Trawienie dokumentów technicznych. Doi: 10.1109/ISSCC.1962.1157368

- (W) TTL Data Book Vol. 2 Texas Instruments 1985

- (W) TTL Data Book Fairchild 1978

- (W) Poziomy napięcia logicznego

- (W) DC Charakterystyka elektryczna MM74HC Szybka logika CMOS , Fairchild 1998 (strona 2, porównanie z LS00)

- (W) Charakterystyka wejściowa i wyjściowa cyfrowych zintegrowanych obwodów , Texas Instruments, 1996

- (W) Texas Instruments Advanced Schottky Family, 1985

- (W) SNX400, SNX4LS00 i SNX4S00 KWADANIE 2 Bramy pozytywne 2-wejściowe , Texas Instruments, 1983 Rev. 2017

- (W) 74ALVT16952 2,5 V/3,3 V 16-bitowy transceiver (3-stanowy) , Philips Semiconductors, 1998

- (W) LS/S/TTL LOGIC DATABOOK National Semiconductor 1989

- (W) TTL Logic – Standard TTL, Schottky, Data Book Schottky o niskiej mocy Texas Instruments 1988

- (W) FAST – Fairchild Advanced Schottky TTL Fairchild 1981

- (W) Advanced Schottky Databook National Semiconductor 1982

- (W) LSI Logic Book Texas Instruments 1986

Powiązane artykuły [[[ modyfikator |. Modyfikator i kod ]

Linki zewnętrzne [[[ modyfikator |. Modyfikator i kod ]

Recent Comments