ストレージモジュール – ウィキペディア

a メモリモジュール また メモリバー いくつかのメモリビルディングブロック(積分回路の形の動的RAM)がはんだ付けされている小さな回路基板です。ストレージモジュールは、コンピューターやプリンターなどの電子デバイスのRAMを形成または拡張し、特別に設計されたスロットに配置されています。

メモリモジュールの指定は、メモリカードまたはUSBスティックにも使用されなくなります。

パーソナルコンピューター用の商用モジュール設計は、または商品です。

- シングルインラインメモリモジュール(SIMM)(これには多くの行があり、それぞれが連絡先で両側に表されています):

- 8ビットワイドモジュール(30の連絡先)

- これは、接続スピンを備えたバリアントでも利用できました。単一のインラインピンパッケージ(SIPP)と呼ばれ、接触面にはんだ付けされた接続ピンを備えたSIMMに実際に対応します。

- PS/2シム、32ビット幅、72の連絡先、

- 8ビットワイドモジュール(30の連絡先)

- デュアルインラインメモリモジュール(DIMM)(ここでは、両側の接触は互いに独立しています。)、幅64ビット、在庫があります。

- 同期動的ランダムアクセスメモリ(SDRAM、SDR)

- ダブルデータレート(DDR-SDRAM、DDR)

- ダブルデータレート2(DDR2-SDRAM、DDR2)

- ダブルデータレート3(DDR3-SDRAM、DDR3)

- ダブルデータレート4(DDR4-SDRAM、DDR4)

- 低スペース要件のための小さなアウトラインデュアルインラインメモリモジュール(SO-DIMM)(たとえば、ノートブックなど)

- マイクロデュアルインラインメモリモジュール(マイクロディム)

- ランバスインラインメモリモジュール(RIMM)、16ビット幅

- 小さなアウトラインベルト(so-belt)

メーカーに依存するモジュール形式(たとえば、サーバーの場合)および特別な要件を求めるモジュールは、edo-ramのDIMMを含む大量に利用できます。一方、他のデバイスタイプ(プリンター、RAIDコントローラー)は、一般的なPCモジュールを使用します。

SIMMメモリモジュール(非同期)は、「登録されていない」または「レジスタ」に従って、「障害のない」または「バッファリング」、DIMMメモリモジュール(同期、SDR、GDR)です。登録されたモジュールのさらなる開発として、DDR2およびDDR3モジュールが完全に緩衝型DIMM(FB-DIMM)として導入されています。

バッファー(バッファー、登録、完全緩衝)は、バッファーの遅延によるアクセスの場合は遅くなりますが、チップセットまたはCPUドロップのメモリインターフェイスの電気荷重は遅くなります。これにより、特にメモリ拡張が大きいサーバーアプリケーションの場合、このようなモジュールが、より多くのメモリモジュールを使用します。

ストレージ容量(サイズ) [ 編集 | ソーステキストを編集します ]

メモリモジュールのストレージ容量は、通常、ほとんど類似したメモリチップとその数のストレージ容量からの製品として生じます。

例:

メモリモジュールには、GM72V16821CT10Kタイプの16個のチップが装備されています。このチップのデータシートでは、524.288(= 2の2つのベンチにあると述べられています。 19 )Wörterはそれぞれ16ビットの幅で編成されています(2×2 19 ×16)。これにより、2×2のチップあたりのストレージ容量が得られます 19 ×16ビット= 2 24 ビット= 16,777.216ビット。これらのチップのうち16個には、2のメモリモジュールのストレージ容量があります 24 ×16 = 2 28 BIT = 268.435.456ビット;バイトごとに8ビットが2です (28-3) byte = 33.554.432 byte = 32 mib。

一部のメモリモジュールには、エラー修正またはパリティ関数のために情報を保存する1つまたは2つの追加のチップ(同じタイプまたはその他のタイプ)があります。ここでは、9ビットがバイト(8つのデータビットと1つのテストビット)によく使用されます。

ケーブル [ 編集 | ソーステキストを編集します ]

今日時代遅れのGDR/DDR2メモリには64があります データ – エリアライン(またはECCで72)に署名します。個々のSDRAMチップは接続されているため、データベースの幅全体を占有します。各チップは、特定のデータラインを担当します。 「× n 「 – 組織化できます n データラインを供給します。 64行のデータバスの場合、64/ n 組織のチップ「× n ” 必要。いくつかのベンチを備えたモジュール(以下を参照)では、いくつかのチップ(2または4)が並行してデータラインに切り替えられます。その結果、モジュールに含まれます k ベンチ64/ n × k 組織のチップ「× n 「。

追加の入力ケーブルは、メモリモジュールの選択を調整します( チップ選択 )およびデータの書き込みまたは読み取り方向(R/W)。

スピード [ 編集 | ソーステキストを編集します ]

サイズと同様に、dimmm全体と個々のチップ全体を区別します。単一のチップは、常に最大クロック周波数(DDR2-1066、DDR-400、SDRAM 133)を指します。

一方、DIM全体は、データ転送速度(PC2-4200、PC3200など)に関するものです。 266 MHzのクロック周波数を持つDDR2-533を備えたSDRAMチップを装備し、GDR2モードでクロックごとに4つのデータ単語を送信し、例、例えば最大透過率を計算できます。

- メモリあたり64行モジュールは、4×8バイト= 32バイトを送信できます。

- 13330万クロックサイクル/s(MHz)×32バイト= 4.266億バイト/s、つまり約4.2 gb/s。

データ転送パフォーマンス値は理想的な値にすぎず、実際には決して達成されません。ただし、ストレージを分類することが一般的です。上記の例では、133 MHzで実行されるGDR2-533チップのPC2-4200です(DDR2-SDRAMを参照)。

ベンチ/ランク [ 編集 | ソーステキストを編集します ]

異なる数の同じモジュールで調光をセットアップできます。 JELC委員会は、DIMMを構築するために非常に具体的な要件を作成しています。 4(バッファーのみ)、8または16のデータ行(上記の行を参照)のいずれかを使用するチップを使用することができます。さらに、DRAMチップスの特定のグループは常に銀行に割り当てられます。銀行またはランク(すべてのミノロジーによる)は、メモリモジュールの明確で独立した64ビットの広範な範囲(ECCモジュール72ビット)です。 [初め] [2] すべての銀行は、個別のメモリモジュールのように動作します。したがって、たとえば、2バンクモジュールは、2つの1バンクモジュールにバスラインに負担をかけます。銀行のメモリモジュール、2つまたは4つのベンチ(シングル、デュアル、クアッドランクディムム)があります。チップセットは通常、最大8つのベンチしか管理できないため(またはGDR-400などの高速ではほとんど6ベンチのみ)、大規模なメモリ拡張のために1袋モジュールに戻る必要があります(たとえば、8×2 GIB = 16 GEBなど)。さらに、そのような場合、通常、RAMの速度を低下させる必要があります。たとえば、PC3200からPC2700まで、ラインの干渉が大きくなりすぎます。

銀行の数と、メモリチップを使用してメモリモジュールの一方的または両側に直接接続されていません(片側/両側)。 H.片側モジュールには、2つのベンチに含まれる可能性があり、両側に装備されているモジュールには1つの銀行のみを含めることができます。

-

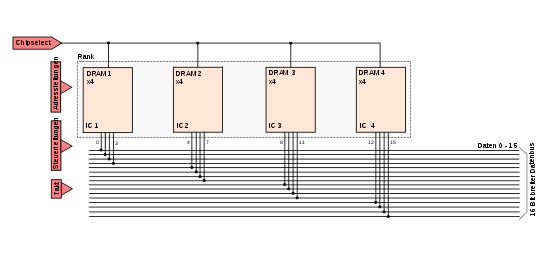

1つの銀行を備えたDRAMモジュール:

銀行は4つのドラムブロックで構成されており、 chipselect – シグナルアクティブ化。 -

2つのベンチ付きDRAMモジュール:

各銀行は、それぞれ4つのデータラインを持つ4つのDRAMブロックで構成されています(×4)。

それぞれの銀行は、 Chipselect 0/1 – 選択されたシグナル。

パフ [ 編集 | ソーステキストを編集します ]

RAMチップは、さまざまなバス幅(4ビット、8ビット、または16ビット)とさまざまなサイズ(2015:4 GBIT、8 GBIT、または16 GBIT)で利用できます。 [3] 。

小さなモジュール(2 GB)の建設には、広いバスを備えたいくつかの小さなRAMチップブロックが必要です(4個の256m×16ビット)。これらの各RAMチップブロックは、アドレスと制御ラインに依存します(これらはここで4です)、

RAMチップモジュールは、データラインに依存します。

大きなRAMモジュールの場合、より大きなRAMチップモジュール(8 GBIT、16 GBIT)およびより多くのコンポーネント(8、16、32)の数(8、16、32)が使用され、それに応じてバスの幅が減少します(8ビット、4ビット)。

チップの数が多いため、アドレスラインと制御ラインのひずみも増加します。 9つのチップから、アドレスラインと制御ラインはレジスタでバッファリングする必要があります。このモジュラータイプは、RDIMM(登録DIMM)と呼ばれます。

すべてのモジュールの合計バス幅が64/72ビットを超える場合、データラインも並行してオンにする必要があります。これにより、推奨または必要なデータラインの追加バッファリングが可能になります。モジュラー型はlrdimm(負荷減少DIMM)です。

| モジュール | メモリモジュール | 扇形に広がります | 備考 | ||

|---|---|---|---|---|---|

| 番号 | タイプ(合計) | 住所・アドレス | データ | ||

| 2 GB | 4× | 256 m ×16ビット( 4 gbit) | 4 | 初め | 最小モジュールMIT DDR4 RAM |

| 4ギガバイト | 8× | 512 m × 8ビット( 4 gbit) | 8 | 初め | より多くのチップによる拡張 |

| 4ギガバイト | 4× | 512 m ×16ビット( 8 gbit) | 4 | 初め | 大きなチップによる拡張 |

| 16ギガバイト | 8× | 2 g × 8ビット(16 gbit) | 8 | 初め | 影響を受けていないDIMM(UDIMM)として利用できる最大のモジュールの8のアドレスのファンアウト |

| 16 GBYTE ECC | 9× | 2 g × 8ビット(16 gbit) | 9 | 初め | ECCのバージョン |

| 32 GB | 16× a | 4 g × 4ビット(16 gbit) | 16 | 初め | 16のアドレスのファンアウトでは、アドレスのバッファリングが必要です(RDIMM:登録DIMM) |

| 32 GBYTE ECC | 18× a | 4 g × 4ビット(16 gbit) | 18 | 初め | ECCのバージョン |

| 64 GBYTE ECC | 36× a | 4 g × 4ビット(16 gbit) | 36 | 2 | 36のアドレスのファンアウトでは、アドレスのバッファリングが必要です(RDIMM:登録DIMM)。 2のデータのファンアウト、データもバッファリングされている場合、それは(lrdimm:負荷減少DIMM)です。 |

登録されたDIMMと荷重減少DIMMは、バッファービルディングブロックの追加のレイテンシにより、より大きなレイテンシを持っています。

アドレス指定の仕組み [ 編集 | ソーステキストを編集します ]

メインメモリのライティングまたは読み取りプロセスのトリガーは、主にCPUです。コンピューター周辺機器もDMAを介してメモリにアクセスすることもできますが、ほとんどの操作はCPUによっても開始されます。

CPUがプロセッサキャッシュ内でデータを見つけられない場合、またはメモリにデータを直接書き込みたい場合、メモリコントローラーが委託されます。などの古いインテルCPUでB.ペンティウム4またはコア2デュオは、ノースブリッジにあるメモリコントローラーにフロントサイドバスを介してコマンドを送信します。メモリコントローラーはCPUに直接配置されているため、K8アーキテクチャの導入以来、コアIシリーズやAMD CPUのモデルなどの新しいIntelプロセッサがより短い方法です。

タイミング [ 編集 | ソーステキストを編集します ]

ストレージの時間動作を制御するさまざまなパラメーターがあります。デフォルトでは、メーカーが設定した時間動作がメモリバーに入力されます。現代のデザインの場合、バーにはEEPROMがあり、BIOSで読み取ることができ、したがって正しい構成を保証します。ユーザーによるこのように調整されたチューニングを通じて、この時間の動作を最適化する試みが行われ、システムがクラッシュする可能性があります。

GDRメモリは、次の種にラベル付けされています。

| スピード | パフ | t cl | t RCD | t RP | SPD-EEPROM-version | ボードバージョン |

|---|---|---|---|---|---|---|

| PC3200 | の | 30 | 3 | 3 | 初め | A1 |

上記の例では、PC3200U-30331-A1パラメーターでRAMが説明されています。最も重要なパラメーターは、モジュールの最大速度です。速度で詳細に説明されているように、「PC3200」はメモリバーをマークし、毎秒32億バイトを提供できます。これは、プロセッサ/チップセットと適切なメモリモジュールの割り当てを決定するのが非常に簡単であることを意味します。 FSB-400プロセッサは、インターフェイスを介して3.2 GB/sのみを送信することもできます。したがって、このため、このメモリは対応するプロセッサに十分です。

「u」は、予期しないダムを表します。ハイフンの後、重要な遅延時間は続き、時計のサイクルで表現されます。

- CASレイテンシ t cl :読み取りコマンドと読み取りデータの保存の間の期間

- RASからCASへの遅延 t RCD :(最小)ライン /銀行をアクティブにすることと、読み取りコマンドまたはライティングコマンドを送信するまでの時間。

- Ras Precharge Time t RP :(最小)ライン /銀行の非アクティブ化と同じ銀行のラインの更新された活性化の間の時間。

GDR-SDRAMには、2、2.5、または3クロックのCLを備えたチップがあります。そのため、CLパラメーターには2桁が必要です(3033は3.0-3の略)。

GDR2メモリは、次の種にラベル付けされています。

| 容量 | dimmm構造 | スピード | パフ | t cl | t RCD | t RP | SPD-EEPROM-version | ボードバージョン |

|---|---|---|---|---|---|---|---|---|

| 512MB | BRXC | PC2-3200 | の | 3 | 3 | 3 | 初め | A1 |

GDR2メモリの場合、整数時間のみが許可されているため、CLは1つだけで指定されています。容量のサイズは、すべての仕様のGDR2メモリを対象としています。さらに、リーゲルのビルド-UPに関する情報が必要です。 「1RX8」は、(X8)SDRAMS(銀行を参照)を含むシングルランクディムを表し、それぞれに8つのデータ接続があります。

興味深いパラメーターは、許容範囲、温度制限値、またはその他の遅延時間を含む動作電圧もあります。 t ras また t RC 。このようなパラメーターは、すべての仕様で正確に定義されているため、特別に表示されません。アクティブ化からプレシャーの期間 t ras オーバークロッカーにとって興味深いので、指定されてうれしいです。それは主に背後にあります t RP ハイフンによって分離されています。 B. PC3200-2022-5。

コマンドレート(1T/2T)もオーバークロッカーにとって興味深いものですが、メモリチップのこの遅延は孤立したプロパティではありません。この待ち時間は、多くのチップがストレージチャネルでアクティブであり、メモリコントローラーのアドレスラインがより強調されている場合に必要です。原則として、最大3ランク(2倍のランクと単一のランク)に1Tで対処でき、コマンドレートを延長するか、クロック周波数を下げる必要があります。

メモリの時間動作の重要なパラメーターは次のとおりです。

Ras-to-Cas-Delay-操作をラップします [ 編集 | ソーステキストを編集します ]

列アドレス選択または列アドレスストロボ、この制御信号は有効な列アドレス中にあります。メモリモジュールは、このアドレスを中間メモリに配置します。

同期DRAM(SDRAM、GDR-SDRAM)にもRASおよびCASの税入がありますが、ここでは即時の機能を失いました。代わりに、すべての制御信号(CKE、RAS、CAS、CAS、WE、CS)の組み合わせは、クロック側面が増加する同期DRAMで評価され、アドレスラインで信号をどのように解釈する必要があるかを決定します。

外部アドレスラインを保存する利点は、列アドレスの可用性が遅れたという形で、明らかな欠点によって相殺されます。ただし、列アドレスは、行アドレスをデコードし、単語行をアクティブにし、ビット管理信号を評価した後にのみ必要です。ただし、この内部プロセスには約15 nsが必要であるため、遅延列アドレスにマイナスの効果がありません。

RASアクティブ時間t ras [ 編集 | ソーステキストを編集します ]

パラメーター t ras (RASパルス幅、アクティブコマンド期間、銀行のアクティブ時間)は、ラインを無効にするためのコマンド(版画、銀行を閉じる)を送信できるコマンドの前に、ライン(または銀行のライン)をアクティブ化した後に通過したに違いない時間を説明します。パラメーターは、単語の線が無効になる前に、ビット管理電圧の補強と情報の再記録をセルで完全に完了する必要があるという事実によって与えられます。

ras precharge time t RP [ 編集 | ソーステキストを編集します ]

パラメーター t RP (Row Precharge Time)は、同じ銀行の行をアクティブにする新しいコマンドの前に、少なくともPrechargeコマンドに従って通過しなければならない時間を説明します。今回は、細胞フィールドのすべての張力(単語管理電圧、読み取りアンプの供給電圧)がオフになり、すべてのラインの張力(特にビットラインの張力)が最初に戻ってくるという条件によって定義されます。レベル。

RASサイクルタイムt RC [ 編集 | ソーステキストを編集します ]

これは、獲物からプリチャルジまでの2つの全体のサイクルの間の時間を説明しています。

ストレージモジュールは、アセンブリに応じて使用できます

- エラー検出なし

- エラー認識(パリティ)

- エラー補正(ECC)

パリティビットを使用した単純なエラー検出の場合、8ビットワード幅が必要になります。その結果、モジュールは9ビット(単純なSIMM)、36ビット(PS/2-SEIMM)、または72ビット幅(通常のDIMM)になります。また、単一の調光では、エラー補正を使用するのに十分なビット幅を提供します(以下を参照)。一方、いくつかの同様のPS/2モジュールを並列に切り替える必要があります。

エラー修正は、マザーボード(チップセットとBIOS)によってもサポートする必要があります。モジュールの追加ビットは、必要な情報を保存する可能性を作成するだけです。

主なメモリエラーを識別する方法はいくつかあります。これらの手順の1つは、米国の数学者リチャードW.ハミングからのものです。エラー補正コード(ECC)は、各メモリラインの64ビットにわたるハッシュ値の一種です。これらの冗長な情報は、メモリコントローラーによって計算され、他の8つのビット(32ビットメモリラインで7ビットがあります)に保存されているため、ECCメモリには1行あたり72ビットがあります。

プロセス自体は、エラーチェックと修正と呼ばれます。

ECCは、すべての1ビットエラーを修正し、すべての2ビットエラーといくつかのマルチビットエラーを認識できます。 ECCメモリは、デスクトップPCではほとんど使用されていません。

エラー検出のさらなる手法は、チップキル、アクティブメモリ、メモリの回復力、またはメモリの襲撃という名前で知られています。

メモリエラーの主な原因は、(以前に疑われたように)放射線をイオン化することではなく、個々の貯蔵セルの問題(例えば、老化や製造の問題による)です。 [4] [5]

CPU(GPU、FPGA …)2、3、4つ、または4つのメモリインターフェイスが、理想的には、データ送信速度、複数、quar、またはメモリインターフェイスの数に応じて2倍にできる場合。

たとえば、AMDのプロセッサAthlon64-FXには2つのメモリインターフェイスがありますが、Socket 754のAthlon64にはメモリインターフェイスが1つしかありません。

| 忙しい | Busbreite | 指定 | データレート | |

|---|---|---|---|---|

| ddr- SDRAM |

133 MHz | 64ビット | PC2100 | 2,133 GB/s |

| 166 MHz | 64ビット | PC2700 | 2,667 GB/s | |

| 200 MHz | 64ビット | PC3200 | 3,200 GB/s | |

| ddr- SDRAM2 |

200 MHz | 64ビット | PC2-3200 | 3,200 GB/s |

| 266 MHz | 64ビット | PC2-4200 | 4,267 GB/s | |

| 333 MHz | 64ビット | PC2-5300 | 5.333 GB/s | |

| 400 MHz | 64ビット | PC2-6400 | 6,400 GB/s | |

| ddr- SDRAM3 |

400 MHz | 64ビット | PC3-6400 | 6,400 GB/s |

| 533 MHz | 64ビット | PC3-8500 | 8,533 GB/s | |

| 666 MHz | 64ビット | PC3-10600 | 10,667 GB/s | |

| 800 MHz | 64ビット | PC3-12800 | 12,800 GB/s | |

| ddr- SDRAM4 |

800 MHz | 64ビット | PC4-12800 | 12,800 GB/s |

| 933 MHz | 64ビット | PC4-14900 | 14,933 GB/s | |

| 1066 MHz | 64ビット | PC4-17100 | 17,067 GB/s | |

| 1200 MHz | 64ビット | PC4-19200 | 19,200 gb/s | |

| 1333 MHz | 64ビット | PC4-21300 | 21,333 GB/s | |

| 1600 MHz | 64ビット | PC4-25600 | 25,600 GB/s | |

| rdram | 400 MHz | 16ビット | PC800 | 1,600 GB/s |

| 533 MHz | 16ビット | PC1066 | 2,133 GB/s | |

| 600 MHz | 16ビット | PC1200 | 2,400 GB/s | |

| 800 MHz | 16ビット | PC1600 | 3,200 GB/s | |

| 1066 MHz | 16ビット | PC2100 | 4,267 GB/s |

データレートの仕様は分類のみに役立つため、ユーザーデータレートには対応しません。

- ↑ メモリランクとIntel E7320 / E7520チップセットベースのサーバー ( 記念 2010年3月31日から インターネットアーカイブ )(PDF; 278 kb)。キングストンテクノロジーメモリランキングテクニカルブリーフ、2005年4月。

- ↑ Corsair DDR2 FAQ ( 記念 の オリジナル 2006年10月11日から インターネットアーカイブ )) 情報: アーカイブリンクは自動的に使用されており、まだチェックされていません。指示に従ってオリジナルとアーカイブのリンクを確認してから、このメモを削除してください。 (PDF; 80 kb)、Februar2004。ランクと銀行の違いは何ですか?

- ↑ https://www.micron.com/products/dram/ddr4-sdram

- ↑ heise.de メインストレージエラーは、以前に想定されていたよりもはるかに頻繁に(2009)

- ↑ cs.toronto.edu (PDF; 284 kb)野生のドラムエラー:大規模なフィールドスタディ、MAI 2009。

Recent Comments