Intel-Haswell-Microarchitechitechur – ウィキペディア

| hasll(microeriteitecture) | |

|---|---|

| メーカー | インテル |

| 製造プロセス | 22 nm |

| ベース | ベース1150 RPGA 947 BGA 1364 BGA 1168 |

| 販売 指定 |

Core i3、4。生成 Core i5、4。生成 Core i7、4。生成 xeon セレロン ペンティウム |

| コア/スレッド | 2–4(デスクトップ) 6+(極端) 8+(xeon) |

| L1-Cache | コアあたり32+32 kb |

| L2-Cache | コアあたり256 kb |

| L3-キャッシュ | 2〜8 MB(分割) |

| L4-Cache | N/Vまたは128 MB(IRIS Proモデル) |

| 前身 | サンディブリッジ(TOCK) アイビーブリッジ(ティック) |

| 後継 | ブロードウェル(ティック) Skylake(tock) |

ハスウェル 2013年の第2四半期にアイビーブリッジアーキテクチャの後継者として公開された、チップメーカーIntelによるプロセッサマイクロアーキテクチャのコード名です。アイビーブリッジのように、ハスウェルは22 nmプロセスに基づいています。統合されたGPUは、DirectX 11.1およびOpenGL 4.0もサポートしています。ベース1150と80年代のチップセットの1つを備えたメインボードが必要です。 90年代シリーズのチップセットは、ハスウェルリフレッシュとも呼ばれる第2世代のハスウェルプロセッサ向けです。

Haswellプロセッサは、IT見本市Computexが開始される数日前の2013年6月1日に正式に発表されました。ただし、中国およびアジアの他の地域の個々のディーラーは、HaswellプロセッサとLGA1150メインボードの販売を早めに始めました。 [初め]

コード名は、米国コロラド州のハスウェル村から派生していました。 [2]

ハスウェルは、特にエネルギー効率とパフォーマンスのために最適化されました。 [3] 22 nmの生産プロセスに切り替えるときに導入された新しいFinfetトランジスタの利点を使用します。 [4]

Haswellプロセッサ用のチップセット [ 編集 | ソーステキストを編集します ]

Haswellプロセッサは、Ivy Bridgeプロセッサのチップセットと互換性がありません。さらに、Intel with Haswellは、より多くのUSB 3.0インターフェイスなどの追加の機器機能を備えた新しいチップセットを導入しています。

説明 [ 編集 | ソーステキストを編集します ]

- ult = 超低熱設計力 ; ulx = 超低極端 TDP。

- 特定のBGAバージョンのみがGT3(Intel HD 5000、Intel Iris 5100)またはGT3E(Intel Iris Pro 5200)が与えられます。他のすべてのモデルは、GT2(Intel HD 4×00)統合グラフィックユニットを受け取ります。 Intel HD Graphicsは詳細情報を提供します。

- ウルトラブックとタブレットには低エネルギー消費が必要なため、Haswell-CultとHaswell-ULXプロセッサはデュアルコアバリアントでのみ利用できます。他のすべてのバージョンは、デュアルまたはクアッドコアモデルです。

パフォーマンス [ 編集 | ソーステキストを編集します ]

Ivy Bridgeと比較して、Haswellにはベクトル処理パフォーマンスが約8%増加し、1つのスレッドパフォーマンスが最大6%優れています。 [5] さらに、Haswellプロセッサは、同等のIvy Bridgeモデルよりも約8%少ない電力を使用しています。 [5] [6] [7] [8] さらに、Ivy Bridge(コアごとに8つの実行ポートの代わりに)と比較して、順次CPUパフォーマンスの改善を6%記録できます。 [5] 主な最適化は統合グラフィックスユニットで実施されました。ここでは、前任者のIntel HD 4000(Haswell HD 4600対Ivy Bridge HD 4000)と比較して20%のパフォーマンスが向上しました。 [5]

Haswellはいくつかのバージョンに登場しました: [9]

Haswell-dt [ 編集 | ソーステキストを編集します ]

デスクトップバージョン(ベースLGA1150)

- VierkernProzessor(Quad-Core)

- L1-Cache:各32 + 32 KIB(データ +手順)

- L2キャッシュ:プロセスの場所を備えた各コア256キブ

- L3-CACHHE:2 MIB BIS 8 MIB

- MMX、SSE、SSE2、SSE3、SSSE3、SSE4.2、Intel 64、EIST、XD-BIT、IVT、AES-Instruktionen、AVX、AVX2、SMT、TXT、収集、BMI1、BMI2、FMA33

- 統合GPU

- ベース1150

- 敷設パフォーマンス(TDP):35–84 w

- 外観日:2013年6月4日

- 製造技術:22 nm

- サイズ:14億トランジスタ(IGPUおよびIntegr。Northbridgeを含む177mm²)

- カプセット:2.3–4.4 GHz

- Modelle:Intel Core i7-4770シリーズ

Haswell-MB [ 編集 | ソーステキストを編集します ]

モバイルバージョン(PGAベース)

ハスウェル(BGAバージョン) [ 編集 | ソーステキストを編集します ]

- 47 W und 57 W TDP: Haswell-h (「オールインワン」システム、Mini-ITXメインボード、およびその他のメインボードの小さなフォームファクターの場合)

- 13,5 W UND 15 W TDP(MCM): Haswell-ult (IntelのUltrabookプラットフォーム用)

- 10 W TDP(SOC): Haswell-ulx (タブレットコンピューターと特定のUltrabookの実装用)

Haswell-e [ 編集 | ソーステキストを編集します ]

ハイエンドデスクトップ(FCLGA2011-3)

- 6コアプロセッサ(ヘキサコア)/8コアプロセッサ(オクタコア)#* L1-キャッシュ:各コア32 + 32 KIB(データ +命令)

- L2キャッシュ:プロセスの場所を備えた各コア256キブ

- L3-CACHHE:15 mib bis 20 mib

- MMX、SSE、SSE2、SSE3、SSSE3、SSE4.2、Intel 64、EIST、XD-BIT、IVT、AES-Instruktionen、AVX、AVX2、SMT、TXT、収集、BMI1、BMI2、FMA33

- ソケット2011-3

- 敷設パフォーマンス(TDP):140 w

- 外観日:2014年8月29日

- 製造技術:22 nm

- サイズ:26億トランジスタ(Integr。Northbridgeを含む)で356mm²

- カプセット:3.0–3.7 GHz

- Modelle:Intel Core i7-5900シリーズ

Haswell-ep [ 編集 | ソーステキストを編集します ]

サーバーバージョン(FCLGA2011-3) [十]

-

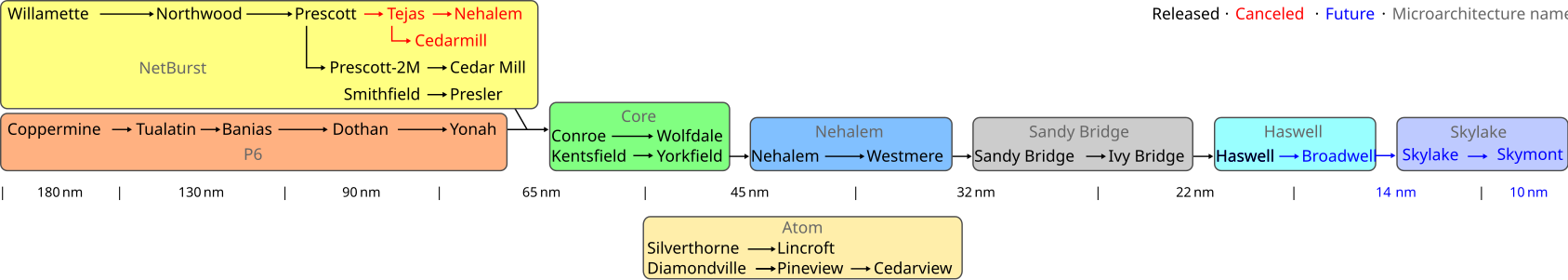

NetburstまたはP6からSkylakeへのIntel-CPUコアプロジェクト計画

- ↑ 中国のHaswellプロセッサは、すでに店舗で利用可能です 。 の: ComputerBase.DE 、2013年5月12日にアクセス。

- ↑ アンディ・ヴォン: コロラドの小さな町ハスウェルにちなんで名付けられたインテルの最新プロセッサ。 の: デンバーポスト。 デジタルファーストメディア、2013年2月6日、 2014年7月17日に取得 (英語)。

- ↑ ライアンシュアウト: IDF 2012:Intel Haswell Architectureが明らかにしました。 の: PCの視点。 2013年9月22日に取得 。

- ↑ IDF:IntelはHaswellがIvy Bridge Transistorsを使用しないと言います 。 ( 記念 2012年9月20日から インターネットアーカイブ ) の: Inquirer

- ↑ a b c d gennadiy shvets: Intel Core I5-3570K対I5-4670K。 2013年7月9日、 2013年7月23日にアクセス 。

- ↑ xbitlabs.com

- ↑ pcpro.co.uk

- ↑ bit-tech.net

- ↑ Intel HaswellとBroadwellシリコンバリアントは詳細です 。 の: TechPowerup

- ↑ 新しいIntel Haswell-Ep (ServerMeile TechNet)

Recent Comments